*P* 53

# 53.1 PACKSSWB/PACKSSDW—Pack with Signed Saturation

| Opcode   | Instruction             | Description                                                                                                                          |

|----------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 0F 63 /r | PACKSSWB mm, mm/<br>m64 | Packs and saturate pack 4 signed words from <i>mm</i> and 4 signed words from <i>mm/m64</i> into 8 signed bytes in <i>mm</i> .       |

| 0F 6B /r | PACKSSDW mm, mm/<br>m64 | Pack and saturate 2 signed doublewords from <i>mm</i> and 2 signed doublewords from <i>mm/m64</i> into 4 signed words in <i>mm</i> . |

#### **Description**

Packs and saturates signed words into bytes (PACKSSWB) or signed doublewords into words (PACKSSDW). The PACKSSWB instruction packs 4 signed words from the destination operand (first operand) and 4 signed words from the source operand (second operand) into 8 signed bytes in the destination operand. If the signed value of a word is beyond the range of a signed byte (that is, greater than 7FH or less than 80H), the saturated byte value of 7FH or 80H, respectively, is stored into the destination.

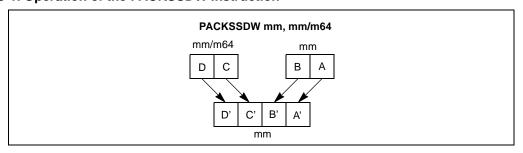

The PACKSSDW instruction packs 2 signed doublewords from the destination operand (first operand) and 2 signed doublewords from the source operand (second operand) into 4 signed words in the destination operand (see Figure 53-1). If the signed value of a doubleword is beyond the range of a signed word (that is, greater than 7FFFH or less than 8000H), the saturated word value of 7FFFH or 8000H, respectively, is stored into the destination.

The destination operand for either the PACKSSWB or PACKSSDW instruction must be an MMX register; the source operand may be either an MMX register or a quadword memory location.

Figure 53-1. Operation of the PACKSSDW Instruction

# Operation

```

IF instruction is PACKSSWB

THEN

DEST(7..0) ← SaturateSignedWordToSignedByte DEST(15..0);

DEST(15..8) ← SaturateSignedWordToSignedByte DEST(31..16);

DEST(23..16) ← SaturateSignedWordToSignedByte DEST(47..32);

DEST(31..24) ← SaturateSignedWordToSignedByte DEST(63..48);

DEST(39..32) ← SaturateSignedWordToSignedByte DEST(63..48);

DEST(47..40) ← SaturateSignedWordToSignedByte SRC(15..0);

DEST(55..48) ← SaturateSignedWordToSignedByte SRC(31..16);

DEST(63..56) ← SaturateSignedWordToSignedByte SRC(47..32);

```

```

\begin{array}{ll} {\tt ELSE}~(*~instruction~is~PACKSSDW~*) \\ & {\tt DEST}(15..0) \leftarrow {\tt SaturateSignedDoublewordToSignedWord~DEST}(31..0); \\ & {\tt DEST}(31..16) \leftarrow {\tt SaturateSignedDoublewordToSignedWord~DEST}(63..32); \\ & {\tt DEST}(47..32) \leftarrow {\tt SaturateSignedDoublewordToSignedWord~SRC}(31..0); \\ & {\tt DEST}(63..48) \leftarrow {\tt SaturateSignedDoublewordToSignedWord~SRC}(63..32); \\ {\tt FI}; \end{array}

```

## Flags Affected

None.

#### **Protected Mode Exceptions**

#GP(0) If a memory operand effective address is outside the CS, DS, ES, FS or GS

segment limit.

#SS(0) If a memory operand effective address is outside the SS segment limit.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made

while the current privilege level is 3.

# **Real-Address Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#### Virtual-8086 Mode Exceptions

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made.

# 53.2 PACKUSWB—Pack with Unsigned Saturation

| Opcode   | Instruction             | Description                                                                                                                |

|----------|-------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 0F 67 /r | PACKUSWB mm, mm/<br>m64 | Pack and saturate 4 signed words from <i>mm</i> and 4 signed words from <i>mm/m64</i> into 8 unsigned bytes in <i>mm</i> . |

## **Description**

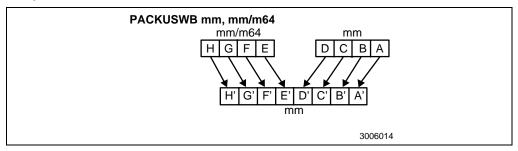

Packs and saturates 4 signed words from the destination operand (first operand) and 4 signed words from the source operand (second operand) into 8 unsigned bytes in the destination operand (see Figure 53-2). If the signed value of a word is beyond the range of an unsigned byte (that is, greater than FFH or less than 00H), the saturated byte value of FFH or 00H, respectively, is stored into the destination.

The destination operand must be an MMX register; the source operand may be either an MMX register or a quadword memory location.

Figure 53-2. Operation of the PACKUSWB Instruction

#### Operation

#### Flags Affected

None.

#### **Protected Mode Exceptions**

| #GP(0)          | If a memory operand effective address is outside the CS, DS, ES, FS or segment limit. |  |

|-----------------|---------------------------------------------------------------------------------------|--|

| #SS(0)          | If a memory operand effective address is outside the SS segment limit.                |  |

| #UD             | If EM in CR0 is set.                                                                  |  |

| #NM             | If TS in CR0 is set.                                                                  |  |

| #MF             | If there is a pending FPU exception.                                                  |  |

| #PF(fault-code) | If a page fault occurs.                                                               |  |

#AC(0) If alignment checking is enabled and an unaligned memory reference is made

while the current privilege level is 3.

## **Real-Address Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#### **Virtual-8086 Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made.

# 53.3 PADDB/PADDW/PADDD—Packed Add

| Opcode   | Instruction          | Description                                                                    |

|----------|----------------------|--------------------------------------------------------------------------------|

| 0F FC /r | PADDB mm, mm/<br>m64 | Add packed bytes from <i>mm/m64</i> to packed bytes in <i>mm</i> .             |

| 0F FD /r | PADDW mm, mm/<br>m64 | Add packed words from <i>mm/m64</i> to packed words in <i>mm</i> .             |

| OF FE /r | PADDD mm, mm/<br>m64 | Add packed doublewords from <i>mm/m64</i> to packed doublewords in <i>mm</i> . |

#### **Description**

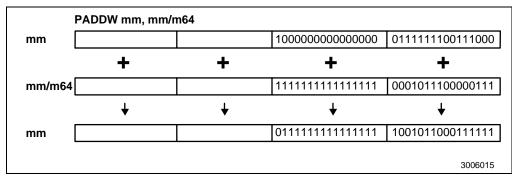

Adds the individual data elements (bytes, words, or doublewords) of the source operand (second operand) to the individual data elements of the destination operand (first operand). (See Figure 53-3.) If the result of an individual addition exceeds the range for the specified data type (overflows), the result is wrapped around, meaning that the result is truncated so that only the lower (least significant) bits of the result are returned (that is, the carry is ignored).

The destination operand must be an MMX register; the source operand can be either an MMX register or a quadword memory location.

Figure 53-3. Operation of the PADDW Instruction

The PADDB instruction adds the bytes of the source operand to the bytes of the destination operand and stores the results to the destination operand. When an individual result is too large to be represented in 8 bits, the lower 8 bits of the result are written to the destination operand and therefore the result wraps around.

The PADDW instruction adds the words of the source operand to the words of the destination operand and stores the results to the destination operand. When an individual result is too large to be represented in 16 bits, the lower 16 bits of the result are written to the destination operand and therefore the result wraps around.

The PADDD instruction adds the doublewords of the source operand to the doublewords of the destination operand and stores the results to the destination operand. When an individual result is too large to be represented in 32 bits, the lower 32 bits of the result are written to the destination operand and therefore the result wraps around.

Note that like the integer ADD instruction, the PADDB, PADDW, and PADDD instructions can operate on either unsigned or signed (two's complement notation) packed integers. Unlike the integer instructions, none of the MMX instructions affect the EFLAGS register. With MMX instructions, there are no carry or overflow flags to indicate when overflow has occurred, so the software must control the range of values or else use the "with saturation" MMX instructions.

#### Operation

```

IF instruction is PADDB

THEN DEST(7..0) \leftarrow DEST(7..0) + SRC(7..0);

DEST(15..8) \leftarrow DEST(15..8) + SRC(15..8);

DEST(23..16) \leftarrow DEST(23..16) + SRC(23..16);

DEST(31..24) \leftarrow DEST(31..24) + SRC(31..24);

DEST(39..32) \leftarrow DEST(39..32) + SRC(39..32);

DEST(47..40) \leftarrow DEST(47..40) + SRC(47..40);

DEST(55..48) \leftarrow DEST(63..56) + SRC(63..56);

ELSEIF instruction is PADDW

THEN

DEST(15..0) \leftarrow DEST(15..0) + SRC(15..0);

DEST(31..16) \leftarrow DEST(31..16) + SRC(11..16);

DEST(47..32) \leftarrow DEST(47..32) + SRC(47..32);

DEST(63..48) \leftarrow DEST(47..32) + SRC(47..32);

DEST(63..48) \leftarrow DEST(43..48) + SRC(63..48);

ELSE (* instruction is PADDD *)

DEST(31..0) \leftarrow DEST(31..0) + SRC(31..0);

DEST(63..32) \leftarrow DEST(63..32) + SRC(63..32);

FI;

```

#### Flags Affected

None.

#### **Protected Mode Exceptions**

#GP(0) If a memory operand effective address is outside the CS, DS, ES, FS or GS

segment limit.

#SS(0) If a memory operand effective address is outside the SS segment limit.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made

while the current privilege level is 3.

#### **Real-Address Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

## **Virtual-8086 Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made.

# 53.4 PADDSB/PADDSW—Packed Add with Saturation

| Opcode   | Instruction           | Description                                                                                  |

|----------|-----------------------|----------------------------------------------------------------------------------------------|

| 0F EC /r | PADDSB mm, mm/<br>m64 | Add signed packed bytes from <i>mm/m64</i> to signed packed bytes in <i>mm</i> and saturate. |

| 0F ED /r | PADDSW mm, mm/<br>m64 | Add signed packed words from <i>mm/m64</i> to signed packed words in <i>mm</i> and saturate. |

# **Description**

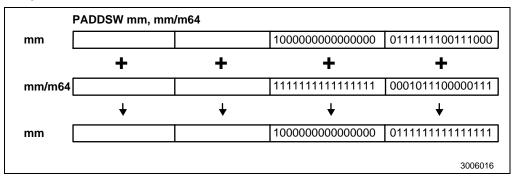

Adds the individual signed data elements (bytes or words) of the source operand (second operand) to the individual signed data elements of the destination operand (first operand). (See Figure 53-4.) If the result of an individual addition exceeds the range for the specified data type, the result is saturated. The destination operand must be an MMX register; the source operand can be either an MMX register or a quadword memory location.

Figure 53-4. Operation of the PADDSW Instruction

The PADDSB instruction adds the signed bytes of the source operand to the signed bytes of the destination operand and stores the results to the destination operand. When an individual result is beyond the range of a signed byte (that is, greater than 7FH or less than 80H), the saturated byte value of 7FH or 80H, respectively, is written to the destination operand.

The PADDSW instruction adds the signed words of the source operand to the signed words of the destination operand and stores the results to the destination operand. When an individual result is beyond the range of a signed word (that is, greater than 7FFFH or less than 8000H), the saturated word value of 7FFFH or 8000H, respectively, is written to the destination operand.

#### Operation

#### Flags Affected

None.

#### **Protected Mode Exceptions**

| #GP(0) | If a memory operand effective address is outside the CS, DS, ES, FS or GS segment limit. |

|--------|------------------------------------------------------------------------------------------|

| #SS(0) | If a memory operand effective address is outside the SS segment limit.                   |

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made

while the current privilege level is 3.

## **Real-Address Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#### Virtual-8086 Mode Exceptions

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made.

# 53.5 PADDUSB/PADDUSW—Packed Add Unsigned with Saturation

| Opcode   | Instruction            | Description                                                                                      |

|----------|------------------------|--------------------------------------------------------------------------------------------------|

| 0F DC /r | PADDUSB mm, mm/<br>m64 | Add unsigned packed bytes from <i>mm/m64</i> to unsigned packed bytes in <i>mm</i> and saturate. |

| 0F DD /r | PADDUSW mm, mm/<br>m64 | Add unsigned packed words from <i>mm/m64</i> to unsigned packed words in <i>mm</i> and saturate. |

#### **Description**

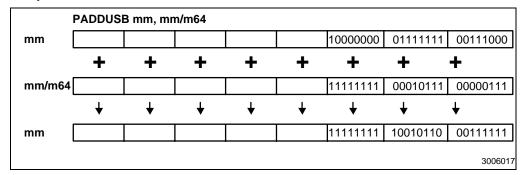

Adds the individual unsigned data elements (bytes or words) of the packed source operand (second operand) to the individual unsigned data elements of the packed destination operand (first operand). (See Figure 53-5.) If the result of an individual addition exceeds the range for the specified unsigned data type, the result is saturated. The destination operand must be an MMX register; the source operand can be either an MMX register or a quadword memory location.

Figure 53-5. Operation of the PADDUSB Instruction

The PADDUSB instruction adds the unsigned bytes of the source operand to the unsigned bytes of the destination operand and stores the results to the destination operand. When an individual result is beyond the range of an unsigned byte (that is, greater than FFH), the saturated unsigned byte value of FFH is written to the destination operand.

The PADDUSW instruction adds the unsigned words of the source operand to the unsigned words of the destination operand and stores the results to the destination operand. When an individual result is beyond the range of an unsigned word (that is, greater than FFFFH), the saturated unsigned word value of FFFFH is written to the destination operand.

# Operation

#### Flags Affected

None.

## **Protected Mode Exceptions**

| #GP(0)          | If a memory operand effective address is outside the CS, DS, ES, FS or C segment limit. |  |

|-----------------|-----------------------------------------------------------------------------------------|--|

| #SS(0)          | If a memory operand effective address is outside the SS segment limit.                  |  |

| #UD             | If EM in CR0 is set.                                                                    |  |

| #NM             | If TS in CR0 is set.                                                                    |  |

| #MF             | If there is a pending FPU exception.                                                    |  |

| #PF(fault-code) | If a page fault occurs.                                                                 |  |

#AC(0) If alignment checking is enabled and an unaligned memory reference is made

while the current privilege level is 3.

## **Real-Address Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#### **Virtual-8086 Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made.

# 53.6 PAND—Logical AND

| Opcode   | Instruction     | Description                                 |

|----------|-----------------|---------------------------------------------|

| 0F DB /r | PAND mm, mm/m64 | AND quadword from mm/m64 to quadword in mm. |

#### **Description**

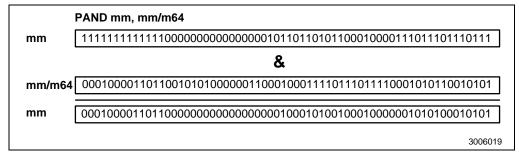

Performs a bitwise logical AND operation on the quadword source (second) and destination (first) operands and stores the result in the destination operand location (see Figure 53-6). The source operand can be an MMX register or a quadword memory location; the destination operand must be an MMX register. Each bit of the result of the PAND instruction is set to 1 if the corresponding bits of the operands are both 1; otherwise it is made zero

Figure 53-6. Operation of the PAND Instruction

#### Operation

DEST ← DEST AND SRC;

#### Flags Affected

None.

#### **Protected Mode Exceptions**

#GP(0) If a memory operand effective address is outside the CS, DS, ES, FS or GS

segment limit.

#SS(0) If a memory operand effective address is outside the SS segment limit.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made

while the current privilege level is 3.

## **Real-Address Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

# Virtual-8086 Mode Exceptions

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made.

# 53.7 PANDN—Logical AND NOT

| Opcode   | Instruction      | Description                                     |

|----------|------------------|-------------------------------------------------|

| 0F DF /r | PANDN mm, mm/m64 | AND quadword from mm/m64 to NOT quadword in mm. |

## **Description**

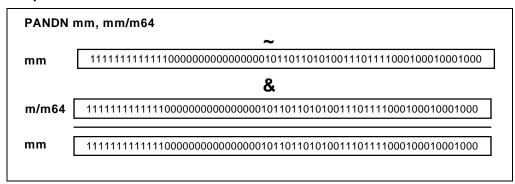

Performs a bitwise logical NOT on the quadword destination operand (first operand). Then, the instruction performs a bitwise logical AND operation on the inverted destination operand and the quadword source operand (second operand). (See Figure 53-7.) Each bit of the result of the AND operation is set to one if the corresponding bits of the source and inverted destination bits are one; otherwise it is set to zero. The result is stored in the destination operand location.

The source operand can be an MMX register or a quadword memory location; the destination operand must be an MMX register.

Figure 53-7. Operation of the PANDN Instruction

#### Operation

DEST ← (NOT DEST) AND SRC;

# Flags Affected

None.

# **Protected Mode Exceptions**

|                 | •                                                                                                                  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------|--|

| #GP(0)          | If a memory operand effective address is outside the CS, DS, ES, FS or GS segment limit.                           |  |

| #SS(0)          | If a memory operand effective address is outside the SS segment limit.                                             |  |

| #UD             | If EM in CR0 is set.                                                                                               |  |

| #NM             | If TS in CR0 is set.                                                                                               |  |

| #MF             | If there is a pending FPU exception.                                                                               |  |

| #PF(fault-code) | If a page fault occurs.                                                                                            |  |

| #AC(0)          | If alignment checking is enabled and an unaligned memory reference is made while the current privilege level is 3. |  |

#### **Real-Address Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

## **Virtual-8086 Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made.

# 53.8 PCMPEQB/PCMPEQW/PCMPEQD—Packed Compare for Equal

| Opcode   | Instruction        | Description                                                                                    |

|----------|--------------------|------------------------------------------------------------------------------------------------|

| 0F 74 /r | PCMPEQB mm, mm/m64 | Compare packed bytes in <i>mm/m64</i> with packed bytes in <i>mm</i> for equality.             |

| 0F 75 /r | PCMPEQW mm, mm/m64 | Compare packed words in <i>mm/m64</i> with packed words in <i>mm</i> for equality.             |

| 0F 76 /r | PCMPEQD mm, mm/m64 | Compare packed doublewords in <i>mm/m64</i> with packed doublewords in <i>mm</i> for equality. |

#### **Description**

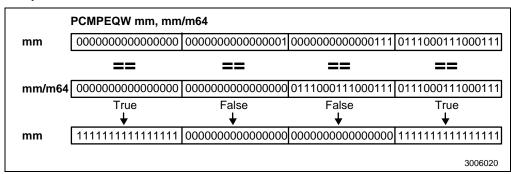

Compares the individual data elements (bytes, words, or doublewords) in the destination operand (first operand) to the corresponding data elements in the source operand (second operand). (See Figure 53-8.) If a pair of data elements are equal, the corresponding data element in the destination operand is set to all ones; otherwise, it is set to all zeros. The destination operand must be an MMX register; the source operand may be either an MMX register or a 64-bit memory location.

Figure 53-8. Operation of the PCMPEQW Instruction

The PCMPEQB instruction compares the bytes in the destination operand to the corresponding bytes in the source operand, with the bytes in the destination operand being set according to the results.

The PCMPEQW instruction compares the words in the destination operand to the corresponding words in the source operand, with the words in the destination operand being set according to the results.

The PCMPEQD instruction compares the doublewords in the destination operand to the corresponding doublewords in the source operand, with the doublewords in the destination operand being set according to the results.

## Operation

#### **Flags Affected**

None:

#### **Protected Mode Exceptions**

#GP(0) If a memory operand effective address is outside the CS, DS, ES, FS or GS segment limit.

#SS(0) If a memory operand effective address is outside the SS segment limit.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made

while the current privilege level is 3.

## **Real-Address Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

## **Virtual-8086 Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made.

# 53.9 PCMPGTB/PCMPGTW/PCMPGTD—Packed Compare for Greater Than

| Opcode   | Instruction            | Description                                                                                         |

|----------|------------------------|-----------------------------------------------------------------------------------------------------|

| 0F 64 /r | PCMPGTB mm, mm/<br>m64 | Compare packed bytes in <i>mm</i> with packed bytes in <i>mm/m64</i> for greater value.             |

| 0F 65 /r | PCMPGTW mm, mm/<br>m64 | Compare packed words in <i>mm</i> with packed words in <i>mm/m64</i> for greater value.             |

| 0F 66 /r | PCMPGTD mm, mm/<br>m64 | Compare packed doublewords in <i>mm</i> with packed doublewords in <i>mm/m64</i> for greater value. |

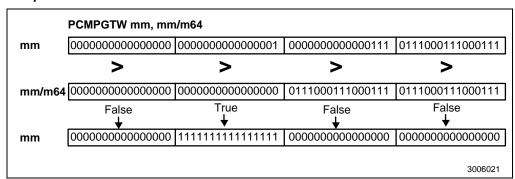

#### **Description**

Compare the individual signed data elements (bytes, words, or doublewords) in the destination operand (first operand) to the corresponding signed data elements in the source operand (second operand). (See Figure 53-9.) If a data element in the destination operand is greater than its

corresponding data element in the source operand, the data element in the destination operand is set to all ones; otherwise, it is set to all zeros. The destination operand must be an MMX register; the source operand may be either an MMX register or a 64-bit memory location.

Figure 53-9. Operation of the PCMPGTW Instruction

The PCMPGTB instruction compares the signed bytes in the destination operand to the corresponding signed bytes in the source operand, with the bytes in the destination operand being set according to the results.

The PCMPGTW instruction compares the signed words in the destination operand to the corresponding signed words in the source operand, with the words in the destination operand being set according to the results.

The PCMPGTD instruction compares the signed doublewords in the destination operand to the corresponding signed doublewords in the source operand, with the doublewords in the destination operand being set according to the results.

#### Operation

#### Flags Affected

None.

#### **Protected Mode Exceptions**

#GP(0) If a memory operand effective address is outside the CS, DS, ES, FS or GS

segment limit.

#SS(0) If a memory operand effective address is outside the SS segment limit.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made

while the current privilege level is 3.

#### **Real-Address Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

## **Virtual-8086 Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made.

# 53.10 PMADDWD—Packed Multiply and Add

| Opcode   | Instruction            | Description                                                                                                                                        |

|----------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 0F F5 /r | PMADDWD mm, mm/<br>m64 | Multiply the packed words in <i>mm</i> by the packed words in <i>mm/m64</i> . Add the 32-bit pairs of results and store in <i>mm</i> as doubleword |

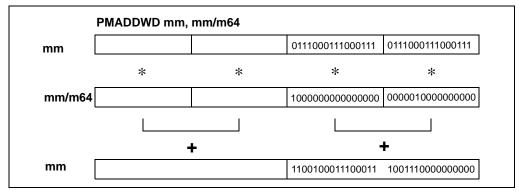

#### **Description**

Multiplies the individual signed words of the destination operand by the corresponding signed words of the source operand, producing four signed, doubleword results (see Figure 53-10). The two doubleword results from the multiplication of the high-order words are added together and stored in the upper doubleword of the destination operand; the two doubleword results from the

multiplication of the low-order words are added together and stored in the lower doubleword of the destination operand. The destination operand must be an MMX register; the source operand may be either an MMX register or a 64-bit memory location.

The PMADDWD instruction wraps around to 80000000H only when all four words of both the source and destination operands are 8000H.

Figure 53-10. Operation of the PMADDWD Instruction

#### Operation

```

\begin{aligned} \text{DEST}(31..0) &\leftarrow (\text{DEST}(15..0) * \text{SRC}(15..0)) + (\text{DEST}(31..16) * \text{SRC}(31..16)); \\ \text{DEST}(63..32) &\leftarrow (\text{DEST}(47..32) * \text{SRC}(47..32)) + (\text{DEST}(63..48) * \text{SRC}(63..48)); \end{aligned}

```

#### Flags Affected

None.

# **Protected Mode Exceptions**

| #GP(0)                          | If a memory operand       | effective addre  | es is outside | the CS D   | S ES ES or GS    |

|---------------------------------|---------------------------|------------------|---------------|------------|------------------|

| $\pi \mathbf{O} \mathbf{I} (0)$ | ii a ilicilioi y opcialio | criccurve addite | oo io Outoiuc | uic Co. Di | 3. LD. I D UI UD |

segment limit.

#SS(0) If a memory operand effective address is outside the SS segment limit.

#UD If EM in CR0 is set. #NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made

while the current privilege level is 3.

#### **Real-Address Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#### Virtual-8086 Mode Exceptions

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made.

# 53.11 PMULHW—Packed Multiply High

| Opcode   | Instruction           | Description                                                                                                                                                         |

|----------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0F E5 /r | PMULHW mm, mm/<br>m64 | Multiply the signed packed words in <i>mm</i> by the signed packed words in <i>mm/m64</i> , then store the high-order word of each doubleword result in <i>mm</i> . |

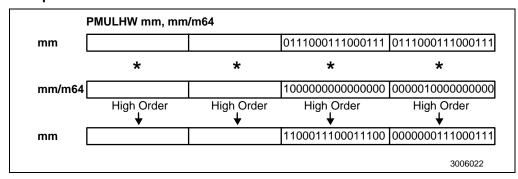

#### **Description**

Multiplies the four signed words of the source operand (second operand) by the four signed words of the destination operand (first operand), producing four signed, doubleword, intermediate results (see Figure 53-11). The high-order word of each intermediate result is then written to its corresponding word location in the destination operand. The destination operand must be an MMX register; the source operand may be either an MMX register or a 64-bit memory location.

Figure 53-11. Operation of the PMULHW Instruction

#### Operation

```

\begin{split} & \mathsf{DEST}(15..0) \leftarrow \mathsf{HighOrderWord}(\mathsf{DEST}(15..0) * \mathsf{SRC}(15..0)); \\ & \mathsf{DEST}(31..16) \leftarrow \mathsf{HighOrderWord}(\mathsf{DEST}(31..16) * \mathsf{SRC}(31..16)); \\ & \mathsf{DEST}(47..32) \leftarrow \mathsf{HighOrderWord}(\mathsf{DEST}(47..32) * \mathsf{SRC}(47..32)); \\ & \mathsf{DEST}(63..48) \leftarrow \mathsf{HighOrderWord}(\mathsf{DEST}(63..48) * \mathsf{SRC}(63..48)); \end{split}

```

#### Flags Affected

None.

#### **Protected Mode Exceptions**

#GP(0) If a memory operand effective address is outside the CS, DS, ES, FS or GS

segment limit.

#SS(0) If a memory operand effective address is outside the SS segment limit.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made

while the current privilege level is 3.

#### **Real-Address Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

## **Virtual-8086 Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made.

# 53.12 PMULLW—Packed Multiply Low

| Opcode   | Instruction           | Description                                                                                                                                            |

|----------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0F D5 /r | PMULLW mm, mm/<br>m64 | Multiply the packed words in <i>mm</i> with the packed words in <i>mm/m64</i> , then store the low-order word of each doubleword result in <i>mm</i> . |

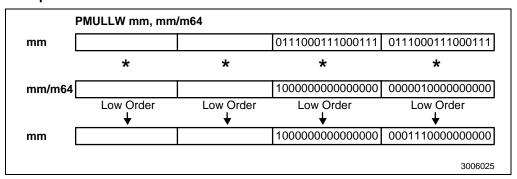

# **Description**

Multiplies the four signed or unsigned words of the source operand (second operand) with the four signed or unsigned words of the destination operand (first operand), producing four doubleword, intermediate results (see Figure 53-12). The low-order word of each intermediate result is then

written to its corresponding word location in the destination operand. The destination operand must be an MMX register; the source operand may be either an MMX register or a 64-bit memory location.

Figure 53-12. Operation of the PMULLW Instruction

#### Operation

```

\begin{array}{lll} \mathtt{DEST}(15..0) \leftarrow \mathtt{LowOrderWord}(\mathtt{DEST}(15..0) * \mathtt{SRC}(15..0)); \\ \mathtt{DEST}(31..16) \leftarrow \mathtt{LowOrderWord}(\mathtt{DEST}(31..16) * \mathtt{SRC}(31..16)); \\ \mathtt{DEST}(47..32) \leftarrow \mathtt{LowOrderWord}(\mathtt{DEST}(47..32) * \mathtt{SRC}(47..32)); \\ \mathtt{DEST}(63..48) \leftarrow \mathtt{LowOrderWord}(\mathtt{DEST}(63..48) * \mathtt{SRC}(63..48)); \end{array}

```

## Flags Affected

None.

# **Protected Mode Exceptions**

| #GP(0) If a memory operand effective address is outside the | CS, DS, ES, FS or GS |

|-------------------------------------------------------------|----------------------|

|-------------------------------------------------------------|----------------------|

segment limit.

#SS(0) If a memory operand effective address is outside the SS segment limit.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made

while the current privilege level is 3.

#### Real-Address Mode Exceptions

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#### **Virtual-8086 Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made.

# 53.13 POP—Pop a Value from the Stack

| Opcode        | Instruction    | Description                                        |

|---------------|----------------|----------------------------------------------------|

| 8F /0         | POP <i>m16</i> | Pop top of stack into m16; increment stack pointer |

| 8F /0         | POP <i>m32</i> | Pop top of stack into m32; increment stack pointer |

| 58+ <i>rw</i> | POP <i>r16</i> | Pop top of stack into r16; increment stack pointer |

| 58+ rd        | POP <i>r32</i> | Pop top of stack into r32; increment stack pointer |

| 1F            | POP DS         | Pop top of stack into DS; increment stack pointer  |

| 07            | POP ES         | Pop top of stack into ES; increment stack pointer  |

| 17            | POP SS         | Pop top of stack into SS; increment stack pointer  |

| 0F A1         | POP FS         | Pop top of stack into FS; increment stack pointer  |

| 0F A9         | POP GS         | Pop top of stack into GS; increment stack pointer  |

#### **Description**

Loads the value from the top of the stack to the location specified with the destination operand and then increments the stack pointer. The destination operand can be a general-purpose register, memory location, or segment register.

The address-size attribute of the stack segment determines the stack pointer size (16 bits or 32 bits—the source address size), and the operand-size attribute of the current code segment determines the amount the stack pointer is incremented (2 bytes or 4 bytes). For example, if these address- and operand-size attributes are 32, the 32-bit ESP register (stack pointer) is incremented by 4 and, if they are 16, the 16-bit SP register is incremented by 2. (The B flag in the stack segment's segment descriptor determines the stack's address-size attribute, and the D flag in the current code segment's segment descriptor, along with prefixes, determines the operand-size attribute and also the address-size attribute of the destination operand.)

If the destination operand is one of the segment registers DS, ES, FS, GS, or SS, the value loaded into the register must be a valid segment selector. In protected mode, popping a segment selector into a segment register automatically causes the descriptor information associated with that segment selector to be loaded into the hidden (shadow) part of the segment register and causes the selector and the descriptor information to be validated (see the "Operation" section below).

A null value (0000-0003) may be popped into the DS, ES, FS, or GS register without causing a general protection fault. However, any subsequent attempt to reference a segment whose corresponding segment register is loaded with a null value causes a general protection exception (#GP). In this situation, no memory reference occurs and the saved value of the segment register is null.

The POP instruction cannot pop a value into the CS register. To load the CS register from the stack, use the RET instruction.

If the ESP register is used as a base register for addressing a destination operand in memory, the POP instruction computes the effective address of the operand after it increments the ESP register. In the case of a 16-bit stack where ESP wraps to 0H as a result of the POP instruction, the resulting location of the memory write is processor family specific.

The POP ESP instruction increments the stack pointer (ESP) before data at the old top of stack is written into the destination.

A POP SS instruction inhibits all interrupts, including the NMI interrupt, until after execution of the next instruction. This action allows sequential execution of POP SS and MOV ESP, EBP instructions without the danger of having an invalid stack during an interrupt<sup>1</sup>. However, use of the LSS instruction is the preferred method of loading the SS and ESP registers.

#### Operation

Loading a segment register while in protected mode results in special checks and actions, as described in the following listing. These checks are performed on the segment selector and the segment descriptor it points to.

POP SS

POP ESE

interrupts may be recognized before the POP ESP executes, because STI also delays interrupts for one instruction.

Note that in a sequence of instructions that individually delay interrupts past the following instruction, only the first instruction in the sequence is guaranteed to delay the interrupt, but subsequent interrupt-delaying instructions may not delay the interrupt. Thus, in the following instruction sequence:

STI

```

THEN #SS(selector);

ELSE

SS ← segment selector;

SS ← segment descriptor;

IF DS, ES, FS or GS is loaded with non-null selector;

THEN

IF segment selector index is outside descriptor table limits

OR segment is not a data or readable code segment

OR ((segment is a data or nonconforming code segment)

AND (both RPL and CPL > DPL))

THEN #GP(selector);

IF segment not marked present

THEN #NP(selector);

\begin{array}{ll} {\tt SegmentRegister} \leftarrow {\tt segment} & {\tt selector}; \\ {\tt SegmentRegister} \leftarrow {\tt segment} & {\tt descriptor}; \end{array}

FI;

IF DS,

ES, FS or GS is loaded with a null selector;

THEN

SegmentRegister ← segment selector;

SegmentRegister ← segment descriptor;

FT;

```

# Flags Affected

None.

#### **Protected Mode Exceptions**

#GP(0) If attempt is made to load SS register with null segment selector.

If the destination operand is in a nonwritable segment.

If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit.

If the DS, ES, FS, or GS register is used to access memory and it contains a null segment selector.

#GP(selector) If segment selector index is outside descriptor table limits.

If the SS register is being loaded and the segment selector's RPL and the segment descriptor's DPL are not equal to the CPL.

If the SS register is being loaded and the segment pointed to is a nonwritable data segment.

If the DS, ES, FS, or GS register is being loaded and the segment pointed to is not a data or readable code segment.

If the DS, ES, FS, or GS register is being loaded and the segment pointed to is a data or nonconforming code segment, but both the RPL and the CPL are greater than the DPL.

#SS(0) If the current top of stack is not within the stack segment.

If a memory operand effective address is outside the SS segment limit.

#SS(selector) If the SS register is being loaded and the segment pointed to is marked not

present.

#NP If the DS, ES, FS, or GS register is being loaded and the segment pointed to is

marked not present.

#PF(fault-code) If a page fault occurs.

#AC(0) If an unaligned memory reference is made while the current privilege level is 3

and alignment checking is enabled.

# **Real-Address Mode Exceptions**

#GP If a memory operand effective address is outside the CS, DS, ES, FS, or GS

segment limit.

#### Virtual-8086 Mode Exceptions

#GP(0) If a memory operand effective address is outside the CS, DS, ES, FS, or GS

segment limit.

#PF(fault-code) If a page fault occurs.

#AC(0) If an unaligned memory reference is made while alignment checking is enabled.

# 53.14 POPA/POPAD—Pop All General-Purpose Registers

| Opcode | Instruction | Description                               |

|--------|-------------|-------------------------------------------|

| 61     | POPA        | Pop DI, SI, BP, BX, DX, CX, and AX        |

| 61     | POPAD       | Pop EDI, ESI, EBP, EBX, EDX, ECX, and EAX |

# **Description**

Pops doublewords (POPAD) or words (POPA) from the stack into the general-purpose registers. The registers are loaded in the following order: EDI, ESI, EBP, EBX, EDX, ECX, and EAX (if the operand-size attribute is 32) and DI, SI, BP, BX, DX, CX, and AX (if the operand-size attribute is 16). (These instructions reverse the operation of the PUSHA/PUSHAD instructions.) The value on the stack for the ESP or SP register is ignored. Instead, the ESP or SP register is incremented after each register is loaded.

The POPA (pop all) and POPAD (pop all double) mnemonics reference the same opcode. The POPA instruction is intended for use when the operand-size attribute is 16 and the POPAD instruction for when the operand-size attribute is 32. Some assemblers may force the operand size to 16 when POPA is used and to 32 when POPAD is used (using the operand-size override prefix [66H] if necessary). Others may treat these mnemonics as synonyms (POPA/POPAD) and use the current setting of the operand-size attribute to determine the size of values to be popped from the stack, regardless of the mnemonic used. (The D flag in the current code segment's segment descriptor determines the operand-size attribute.)

#### Operation

```

IF OperandSize = 32 (* instruction = POPAD *)

THEN

EDI ← Pop();

ESI ← Pop();

EBP ← Pop();

increment ESP by 4 (* skip next 4 bytes of stack *)

EBX ← Pop();

EDX ← Pop();

ECX ← Pop();

EXX ← Pop();

EAX ← Pop();

EAX ← Pop();

EAX ← Pop();

SI ← Pop();

SI ← Pop();

BP ← Pop();

```

```

increment ESP by 2 (* skip next 2 bytes of stack *) BX \leftarrow Pop(); DX \leftarrow Pop(); CX \leftarrow Pop(); AX \leftarrow Pop();

```

#### Flags Affected

None.

#### **Protected Mode Exceptions**

#SS(0) If the starting or ending stack address is not within the stack segment.

#PF(fault-code) If a page fault occurs.

#AC(0) If an unaligned memory reference is made while the current privilege level is 3

and alignment checking is enabled.

#### **Real-Address Mode Exceptions**

#SS If the starting or ending stack address is not within the stack segment.

#### **Virtual-8086 Mode Exceptions**

#SS(0) If the starting or ending stack address is not within the stack segment.

#PF(fault-code) If a page fault occurs.

#AC(0) If an unaligned memory reference is made while alignment checking is enabled.

# 53.15 POPF/POPFD—Pop Stack into EFLAGS Register

| Opcode | Instruction | Description                                   |

|--------|-------------|-----------------------------------------------|

| 9D     | POPF        | Pop top of stack into lower 16 bits of EFLAGS |

| 9D     | POPFD       | Pop top of stack into EFLAGS                  |

#### **Description**

Pops a doubleword (POPFD) from the top of the stack (if the current operand-size attribute is 32) and stores the value in the EFLAGS register or pops a word from the top of the stack (if the operand-size attribute is 16) and stores it in the lower 16 bits of the EFLAGS register (that is, the FLAGS register). (These instructions reverse the operation of the PUSHF/PUSHFD instructions.)

The POPF (pop flags) and POPFD (pop flags double) mnemonics reference the same opcode. The POPF instruction is intended for use when the operand-size attribute is 16 and the POPFD instruction for when the operand-size attribute is 32. Some assemblers may force the operand size to 16 when POPF is used and to 32 when POPFD is used. Others may treat these mnemonics as synonyms (POPF/POPFD) and use the current setting of the operand-size attribute to determine the size of values to be popped from the stack, regardless of the mnemonic used.

The effect of the POPF/POPFD instructions on the EFLAGS register changes slightly, depending on the mode of operation of the processor. When the processor is operating in protected mode at privilege level 0 (or in real-address mode, which is equivalent to privilege level 0), all the non-reserved flags in the EFLAGS register except the VIP, VIF, and VM flags can be modified. The VIP and VIF flags are cleared, and the VM flag is unaffected.

When operating in protected mode, with a privilege level greater than 0, but less than or equal to IOPL, all the flags can be modified except the IOPL field and the VIP, VIF, and VM flags. Here, the IOPL flags are unaffected, the VIP and VIF flags are cleared, and the VM flag is unaffected. The interrupt flag (IF) is altered only when executing at a level at least as privileged as the IOPL. If a POPF/POPFD instruction is executed with insufficient privilege, an exception does not occur, but the privileged bits do not change.

When operating in virtual-8086 mode, the I/O privilege level (IOPL) must be equal to 3 to use POPF/POPFD instructions and the VM, RF, IOPL, VIP, and VIF flags are unaffected. If the IOPL is less than 3, the POPF/POPFD instructions cause a general-protection exception (#GP).

See "EFLAGS Register", for information about the EFLAGS registers.

#### Operation

```

IF VM=0 (* Not in Virtual-8086 Mode *)

THEN IF CPL=0

THEN

IF OperandSize = 32;

EFLAGS ← Pop();

All non-reserved flags except VIP, VIF, and VM can be modified; *)

(* VIP and VIF are cleared; VM is unaffected*)

ELSE (* OperandSize = 16 *)

EFLAGS[15:0] ← Pop(); (* All non-reserved flags can be modified; *)

FI;

ELSE (* CPL > 0 *)

IF OperandSize = 32;

THEN

EFLAGS ← Pop()

All non-reserved bits except IOPL, VIP, and VIF can be modified; *)

(* AII non-reserved bits except LOPE, VIP, and VIF can be modified;

(* IOPL is unaffected; VIP and VIF are cleared; VM is unaffected *)

ELSE (* OperandSize = 16 *)

EFLAGS[15:0] \leftarrow Pop();

All non-reserved bits except IOPL can be modified *)

(* IOPL is unaffected *)

FI;

FI;

(* In Virtual-8086 Mode *)

IF IOPL=3

THEN IF OperandSize=32

THEN

EFLAGS ← Pop()

(* All non-reserved bits except VM, RF, IOPL, VIP, and VIF *)

(* can be modified; VM, RF, IOPL, VIP, and VIF are unaffected *)

ELSE

EFLAGS[15:0] \leftarrow Pop()

All non-reserved bits except IOPL can be modified *)

(* IOPL is unaffected *)

ELSE (* IOPL < 3 *)

#GP(0); (* trap to virtual-8086 monitor *)

FT;

FT;

```

#### Flags Affected

All flags except the reserved bits and the VM bit.

#### **Protected Mode Exceptions**

#SS(0) If the top of stack is not within the stack segment.

#PF(fault-code) If a page fault occurs.

#AC(0) If an unaligned memory reference is made while the current privilege level is 3

and alignment checking is enabled.

#### **Real-Address Mode Exceptions**

#SS If the top of stack is not within the stack segment.

#### **Virtual-8086 Mode Exceptions**

#GP(0) If the I/O privilege level is less than 3.

If an attempt is made to execute the POPF/POPFD instruction with an operand-

size override prefix.

#SS(0) If the top of stack is not within the stack segment.

#PF(fault-code) If a page fault occurs.

#AC(0) If an unaligned memory reference is made while alignment checking is enabled.

# 53.16 POR—Bitwise Logical OR

| Opcode   | Instruction    | Description                                |

|----------|----------------|--------------------------------------------|

| 0F EB /r | POR mm, mm/m64 | OR quadword from mm/m64 to quadword in mm. |

# **Description**

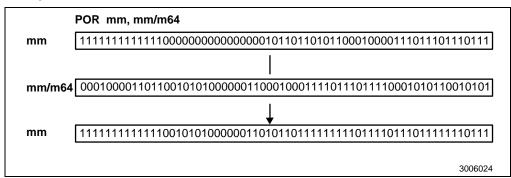

Performs a bitwise logical OR operation on the quadword source (second) and destination (first) operands and stores the result in the destination operand location (see Figure 53-13). The source operand can be an MMX register or a quadword memory location; the destination operand must be an MMX register. Each bit of the result is made 0 if the corresponding bits of both operands are 0; otherwise the bit is set to 1.

Figure 53-13. Operation of the POR Instruction.

#### Operation

$\texttt{DEST} \; \leftarrow \; \texttt{DEST} \; \; \texttt{OR} \; \; \texttt{SRC};$

## Flags Affected

None.

#### **Protected Mode Exceptions**

#GP(0) If a memory operand effective address is outside the CS, DS, ES, FS or GS

segment limit.

#SS(0) If a memory operand effective address is outside the SS segment limit.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made

while the current privilege level is 3.

#### Real-Address Mode Exceptions

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#### Virtual-8086 Mode Exceptions

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made.

# 53.17 PSLLW/PSLLD/PSLLQ—Packed Shift Left Logical

| Opcode       | Instruction      | Description                                                                                         |

|--------------|------------------|-----------------------------------------------------------------------------------------------------|

| 0F F1 /r     | PSLLW mm, mm/m64 | Shift words in <i>mm</i> left by amount specified in <i>mm/m64</i> , while shifting in zeros.       |

| 0F 71 /6, ib | PSLLW mm, imm8   | Shift words in mm left by imm8, while shifting in zeros.                                            |

| 0F F2 /r     | PSLLD mm, mm/m64 | Shift doublewords in <i>mm</i> left by amount specified in <i>mm/m64</i> , while shifting in zeros. |

| 0F 72 /6 ib | PSLLD mm, imm8   | Shift doublewords in <i>mm</i> by <i>imm8</i> , while shifting in zeros.             |

|-------------|------------------|--------------------------------------------------------------------------------------|

| 0F F3 /r    | PSLLQ mm, mm/m64 | Shift <i>mm</i> left by amount specified in <i>mm/m64</i> , while shifting in zeros. |

| 0F 73 /6 ib | PSLLQ mm, imm8   | Shift mm left by Imm8, while shifting in zeros.                                      |

#### **Description**

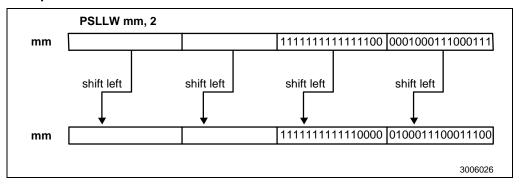

Shifts the bits in the data elements (words, doublewords, or quadword) in the destination operand (first operand) to the left by the number of bits specified in the unsigned count operand (second operand). (See Figure 53-14.) The result of the shift operation is written to the destination operand. As the bits in the data elements are shifted left, the empty low-order bits are cleared (set to zero). If the value specified by the count operand is greater than 15 (for words), 31 (for doublewords), or 63 (for a quadword), then the destination operand is set to all zeros.

The destination operand must be an MMX register; the count operand can be either an MMX register, a 64-bit memory location, or an 8-bit immediate.

The PSLLW instruction shifts each of the four words of the destination operand to the left by the number of bits specified in the count operand; the PSLLD instruction shifts each of the two doublewords of the destination operand; and the PSLLQ instruction shifts the 64-bit quadword in the destination operand. As the individual data elements are shifted left, the empty low-order bit positions are filled with zeros.

Figure 53-14. Operation of the PSLLW Instruction

#### Operation

```

IF instruction is PSLLW THEN  \begin{array}{c} \text{THEN} \\ \text{DEST}(15..0) \leftarrow \text{DEST}(15..0) << \text{COUNT}; \\ \text{DEST}(31..16) \leftarrow \text{DEST}(31..16) << \text{COUNT}; \\ \text{DEST}(47..32) \leftarrow \text{DEST}(47..32) << \text{COUNT}; \\ \text{DEST}(63..48) \leftarrow \text{DEST}(63..48) << \text{COUNT}; \\ \text{ELSE IF instruction is PSLLD} \\ \text{THEN } \{ \\ \text{DEST}(31..0) \leftarrow \text{DEST}(31..0) << \text{COUNT}; \\ \text{DEST}(63..32) \leftarrow \text{DEST}(63..32) << \text{COUNT}; \\ \text{ELSE } (* \text{instruction is PSLLQ *}) \\ \text{DEST} \leftarrow \text{DEST} << \text{COUNT}; \\ \end{array}

```

# Flags Affected

None.

#### **Protected Mode Exceptions**

#GP(0) If a memory operand effective address is outside the CS, DS, ES, FS or GS

segment limit.

#SS(0) If a memory operand effective address is outside the SS segment limit.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made

while the current privilege level is 3.

#### **Real-Address Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

## **Virtual-8086 Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made.

# 53.18 PSRAW/PSRAD—Packed Shift Right Arithmetic

| Opcode      | Instruction          | Description                                                                                            |

|-------------|----------------------|--------------------------------------------------------------------------------------------------------|

| 0F E1 /r    | PSRAW mm, mm/<br>m64 | Shift words in <i>mm</i> right by amount specified in <i>mm/m64</i> while shifting in sign bits.       |

| 0F 71 /4 ib | PSRAW mm, imm8       | Shift words in <i>mm</i> right by <i>imm8</i> while shifting in sign bits                              |

| 0F E2 /r    | PSRAD mm, mm/<br>m64 | Shift doublewords in <i>mm</i> right by amount specified in <i>mm/m64</i> while shifting in sign bits. |

| 0F 72 /4 ib | PSRAD mm, imm8       | Shift doublewords in <i>mm</i> right by <i>imm8</i> while shifting in sign bits.                       |

#### **Description**

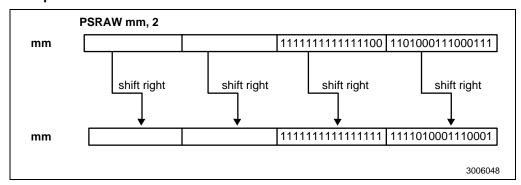

Shifts the bits in the data elements (words or doublewords) in the destination operand (first operand) to the right by the amount of bits specified in the unsigned count operand (second operand). (See Figure 53-15.) The result of the shift operation is written to the destination operand. The empty high-order bits of each element are filled with the initial value of the sign bit of the data element. If the value specified by the count operand is greater than 15 (for words) or 31 (for doublewords), each destination data element is filled with the initial value of the sign bit of the element.

The destination operand must be an MMX register; the count operand (source operand) can be either an MMX register, a 64-bit memory location, or an 8-bit immediate.

The PSRAW instruction shifts each of the four words in the destination operand to the right by the number of bits specified in the count operand; the PSRAD instruction shifts each of the two doublewords in the destination operand. As the individual data elements are shifted right, the empty high-order bit positions are filled with the sign value.

Figure 53-15. Operation of the PSRAW Instruction

## Operation

```

IF instruction is PSRAW THEN  \begin{array}{c} \text{THEN} \\ \text{DEST}(15..0) \leftarrow \text{SignExtend (DEST}(15..0) >> \text{COUNT}); \\ \text{DEST}(31..16) \leftarrow \text{SignExtend (DEST}(31..16) >> \text{COUNT}); \\ \text{DEST}(47..32) \leftarrow \text{SignExtend (DEST}(47..32) >> \text{COUNT}); \\ \text{DEST}(63..48) \leftarrow \text{SignExtend (DEST}(63..48) >> \text{COUNT}); \\ \text{ELSE } \big\{ \text{ (*instruction is PSRAD *)} \\ \text{DEST}(31..0) \leftarrow \text{SignExtend (DEST}(31..0) >> \text{COUNT}); \\ \text{DEST}(63..32) \leftarrow \text{SignExtend (DEST}(63..32) >> \text{COUNT}); \\ \end{array}

```

#### Flags Affected

None.

#### **Protected Mode Exceptions**

| #GP(0) | If a memory operand effective address is outside the CS, DS, ES, FS or GS segment limit. |

|--------|------------------------------------------------------------------------------------------|

| #SS(0) | If a memory operand effective address is outside the SS segment limit.                   |

| #UD    | If EM in CR0 is set.                                                                     |

| #NM    | If TS in CR0 is set.                                                                     |

| #MF    | If there is a pending FPU exception.                                                     |

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made

while the current privilege level is 3.

#### **Real-Address Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

### **Virtual-8086 Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made.

# 53.19 PSRLW/PSRLD/PSRLQ—Packed Shift Right Logical

| Opcode      | Instruction      | Description                                                                                        |  |

|-------------|------------------|----------------------------------------------------------------------------------------------------|--|

| 0F D1 /r    | PSRLW mm, mm/m64 | Shift words in <i>mm</i> right by amount specified in <i>mm/m64</i> while shifting in zeros.       |  |

| 0F 71 /2 ib | PSRLW mm, imm8   | Shift words in mm right by imm8.                                                                   |  |

| 0F D2 /r    | PSRLD mm, mm/m64 | Shift doublewords in <i>mm</i> right by amount specified in <i>mm/m64</i> while shifting in zeros. |  |

| 0F 72 /2 ib | PSRLD mm, imm8   | Shift doublewords in mm right by imm8.                                                             |  |

| 0F D3 /r    | PSRLQ mm, mm/m64 | Shift <i>mm</i> right by amount specified in <i>mm/m64</i> while shifting in zeros.                |  |

| 0F 73 /2 ib | PSRLQ mm, imm8   | Shift mm right by imm8 while shifting in zeros.                                                    |  |

#### **Description**

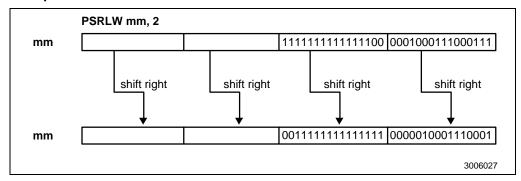

Shifts the bits in the data elements (words, doublewords, or quadword) in the destination operand (first operand) to the right by the number of bits specified in the unsigned count operand (second operand). (See Figure 53-16.) The result of the shift operation is written to the destination operand. As the bits in the data elements are shifted right, the empty high-order bits are cleared (set to zero). If the value specified by the count operand is greater than 15 (for words), 31 (for doublewords), or 63 (for a quadword), then the destination operand is set to all zeros.

The destination operand must be an MMX register; the count operand can be either an MMX register, a 64-bit memory location, or an 8-bit immediate.

The PSRLW instruction shifts each of the four words of the destination operand to the right by the number of bits specified in the count operand; the PSRLD instruction shifts each of the two doublewords of the destination operand; and the PSRLQ instruction shifts the 64-bit quadword in the destination operand. As the individual data elements are shifted right, the empty high-order bit positions are filled with zeros.

Figure 53-16. Operation of the PSRLW Instruction

#### Operation

```

IF instruction is PSRLW THEN {  \begin{array}{c} \text{DEST}(15..0) \leftarrow \text{DEST}(15..0) >> \text{COUNT;} \\ \text{DEST}(31..16) \leftarrow \text{DEST}(31..16) >> \text{COUNT;} \\ \text{DEST}(47..32) \leftarrow \text{DEST}(47..32) >> \text{COUNT;} \\ \text{DEST}(63..48) \leftarrow \text{DEST}(63..48) >> \text{COUNT;} \\ \text{ELSE IF instruction is PSRLD} \\ \text{THEN } \{ \\ \text{DEST}(31..0) \leftarrow \text{DEST}(31..0) >> \text{COUNT;} \\ \text{DEST}(63..32) \leftarrow \text{DEST}(63..32) >> \text{COUNT;} \\ \text{ELSE } (* \text{instruction is PSRLQ *}) \\ \text{DEST} \leftarrow \text{DEST} >> \text{COUNT;} \\ \end{array}

```

#### Flags Affected

None.

#### **Protected Mode Exceptions**

#GP(0) If a memory operand effective address is outside the CS, DS, ES, FS or GS

segment limit.

#SS(0) If a memory operand effective address is outside the SS segment limit.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made

while the current privilege level is 3.

#### **Real-Address Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#### Virtual-8086 Mode Exceptions

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made.

# 53.20 PSUBB/PSUBW/PSUBD—Packed Subtract

| Opcode   | Instruction          | Description                                                                         |

|----------|----------------------|-------------------------------------------------------------------------------------|

| 0F F8 /r | PSUBB mm, mm/<br>m64 | Subtract packed bytes in <i>mm/m64</i> from packed bytes in <i>mm</i> .             |

| 0F F9 /r | PSUBW mm, mm/<br>m64 | Subtract packed words in <i>mm/m64</i> from packed words in <i>mm</i> .             |

| 0F FA /r | PSUBD mm, mm/<br>m64 | Subtract packed doublewords in <i>mm/m64</i> from packed doublewords in <i>mm</i> . |

#### **Description**

Subtracts the individual data elements (bytes, words, or doublewords) of the source operand (second operand) from the individual data elements of the destination operand (first operand). (See Figure 53-17.) If the result of a subtraction exceeds the range for the specified data type (overflows), the result is wrapped around, meaning that the result is truncated so that only the lower (least significant) bits of the result are returned (that is, the carry is ignored).

The destination operand must be an MMX register; the source operand can be either an MMX register or a quadword memory location.

Figure 53-17. Operation of the PSUBW Instruction

The PSUBB instruction subtracts the bytes of the source operand from the bytes of the destination operand and stores the results to the destination operand. When an individual result is too large to be represented in 8 bits, the lower 8 bits of the result are written to the destination operand and therefore the result wraps around.

The PSUBW instruction subtracts the words of the source operand from the words of the destination operand and stores the results to the destination operand. When an individual result is too large to be represented in 16 bits, the lower 16 bits of the result are written to the destination operand and therefore the result wraps around.

The PSUBD instruction subtracts the doublewords of the source operand from the doublewords of the destination operand and stores the results to the destination operand. When an individual result is too large to be represented in 32 bits, the lower 32 bits of the result are written to the destination operand and therefore the result wraps around.

Note that like the integer SUB instruction, the PSUBB, PSUBW, and PSUBD instructions can operate on either unsigned or signed (two's complement notation) packed integers. Unlike the integer instructions, none of the MMX instructions affect the EFLAGS register. With MMX instructions, there are no carry or overflow flags to indicate when overflow has occurred, so the software must control the range of values or else use the "with saturation" MMX instructions.

#### Operation

```

IF instruction is PSUBB

THEN

DEST(7..0) \leftarrow DEST(7..0) - SRC(7..0);

DEST(15..8) \leftarrow DEST(15..8) - SRC(15..8);

DEST(23..16) \leftarrow DEST(23..16) - SRC(23..16);

DEST(31..24) \leftarrow DEST(31..24) - SRC(31..24);

DEST(39..32) \leftarrow DEST(39..32) - SRC(39..32);

DEST(47..40) \leftarrow DEST(47..40) - SRC(47..40);

DEST(55..48) \leftarrow DEST(55..48) - SRC(55..48);

DEST(55..48) \leftarrow DEST(63..56) - SRC(63..56);

ELSEIF instruction is PSUBW

THEN

DEST(15..0) \leftarrow DEST(15..0) - SRC(15..0);

DEST(31..16) \leftarrow DEST(31..16) - SRC(31..16);

DEST(47..32) \leftarrow DEST(47..32) - SRC(47..32);

DEST(63..48) \leftarrow DEST(63..48) - SRC(63..48);

ELSE \{ (* instruction is PSUBD *)

DEST(31..0) \leftarrow DEST(31..0) - SRC(31..0);

DEST(63..32) \leftarrow DEST(63..32) - SRC(63..32);

FI;

```

#### Flags Affected

None.

#### **Protected Mode Exceptions**

| #GP(0) | If a memory operand | effective address | s is outside the C | S. DS. ES. FS or GS |

|--------|---------------------|-------------------|--------------------|---------------------|

|        |                     |                   |                    |                     |

segment limit.

#SS(0) If a memory operand effective address is outside the SS segment limit.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made

while the current privilege level is 3.

#### **Real-Address Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

### **Virtual-8086 Mode Exceptions**

#GP If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If EM in CR0 is set.

#NM If TS in CR0 is set.

#MF If there is a pending FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) If alignment checking is enabled and an unaligned memory reference is made.

# 53.21 PSUBSB/PSUBSW—Packed Subtract with Saturation

| Opcode   | Instruction           | Description                                                                                       |

|----------|-----------------------|---------------------------------------------------------------------------------------------------|

| 0F E8 /r | PSUBSB mm, mm/<br>m64 | Subtract signed packed bytes in <i>mm/m64</i> from signed packed bytes in <i>mm</i> and saturate. |

| 0F E9 /r | PSUBSW mm, mm/<br>m64 | Subtract signed packed words in <i>mm/m64</i> from signed packed words in <i>mm</i> and saturate. |

#### **Description**

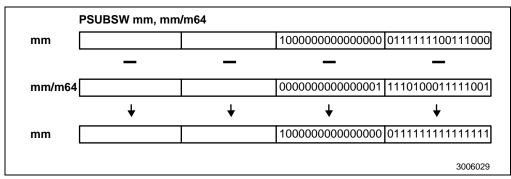

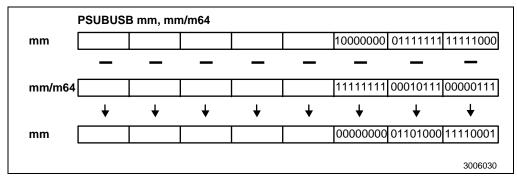

Subtracts the individual signed data elements (bytes or words) of the source operand (second operand) from the individual signed data elements of the destination operand (first operand). (See Figure 53-18.) If the result of a subtraction exceeds the range for the specified data type, the result is saturated. The destination operand must be an MMX register; the source operand can be either an MMX register or a quadword memory location.

Figure 53-18. Operation of the PSUBSW Instruction

The PSUBSB instruction subtracts the signed bytes of the source operand from the signed bytes of the destination operand and stores the results to the destination operand. When an individual result is beyond the range of a signed byte (that is, greater than 7FH or less than 80H), the saturated byte value of 7FH or 80H, respectively, is written to the destination operand.

The PSUBSW instruction subtracts the signed words of the source operand from the signed words of the destination operand and stores the results to the destination operand. When an individual result is beyond the range of a signed word (that is, greater than 7FFFH or less than 8000H), the saturated word value of 7FFFH or 8000H, respectively, is written to the destination operand.

#### **Operation**

```

IF instruction is PSUBSB

THEN

DEST(7..0) ← SaturateToSignedByte(DEST(7..0) - SRC (7..0));

DEST(15..8) ← SaturateToSignedByte(DEST(15..8) - SRC(15..8));

DEST(23..16) ← SaturateToSignedByte(DEST(23..16) - SRC(23..16));

DEST(31..24) ← SaturateToSignedByte(DEST(31..24) - SRC(31..24));

DEST(39..32) ← SaturateToSignedByte(DEST(39..32) - SRC(39..32));

DEST(47..40) ← SaturateToSignedByte(DEST(49..30) - SRC(47..40));

DEST(55..48) ← SaturateToSignedByte(DEST(55..48) - SRC(55..48));

DEST(63..56) ← SaturateToSignedByte(DEST(63..56) - SRC(63..56))

ELSE (* instruction is PSUBSW *)

DEST(15..0) ← SaturateToSignedWord(DEST(15..0) - SRC(15..0));

DEST(31..16) ← SaturateToSignedWord(DEST(31..16) - SRC(31..16));

DEST(47..32) ← SaturateToSignedWord(DEST(47..32) - SRC(47..32));

DEST(63..48) ← SaturateToSignedWord(DEST(63..48) - SRC(63..48));

FI;

```

#### Flags Affected

None.

#### **Protected Mode Exceptions**

| #GP(0)          | If a memory operand effective address is outside the CS, DS, ES, FS or GS segment limit. |

|-----------------|------------------------------------------------------------------------------------------|

| #SS(0)          | If a memory operand effective address is outside the SS segment limit.                   |

| #UD             | If EM in CR0 is set.                                                                     |

| #NM             | If TS in CR0 is set.                                                                     |

| #MF             | If there is a pending FPU exception.                                                     |

| #PF(fault-code) | If a page fault occurs.                                                                  |

#AC(0) If alignment checking is enabled and an unaligned memory reference is made

while the current privilege level is 3.

# **Real-Address Mode Exceptions**